Closely coupled power planes

- Atli

- Dec 12, 2019

- 7 min read

This week I wanted to discuss a topic which is not always fully appreciated by electronics and PCB designers, namely the properties of closely coupled power planes.

So, what are closely coupled power planes? And why do we care? In order to answer the first question we will look at PCB stackups and how they form the closely coupled power planes we want. For the second question we will look at the subject of power delivery networks (PDNs) and briefly mention the benefits that can be achieved by using closely coupled power planes. In our discussion we will make the assumption that any plane is purely an unbroken single net, and that our board is 50[mm] x 50[mm].

PCB stackups

Closely coupled power planes are planes which are positioned close enough to each other that they are significantly capacitively coupled. I have deliberately been vague and used the word significantly because in electronics there are no absolutes and what significantly means is application dependant.

In this section we will go through some more details of how this is achieved.

In the above figure you can see a four-layer stackup. Typically, this stackup will use a core consisting of the L2 Conductor, the middle dielectric, and the L3 Conductor. It will then have a prepreg added on both sides followed by the top and bottom conductor. Alternatively, it could use two cores and a prepreg between the cores, but this is process dependant. In our configuration L2 Conductor and L3 Conductor will typically be spaced such that they provide reference planes to the top and bottom conductors, i.e. they will be closer to the edges than the middle. Our assumption is that there are only two nets on L2 Conductor and L3 Conductor, GND and PWR respectively.

Using a standard stackup from our preferred PCB supplier’s data we can see the dielectric prepregs between the top and L2 and the bottom and L3 are the same thickness. This is done for symmetry, helping with the manufacturing of the board.

Capacitive coupling of planes

Looking at the two planes in the middle you will see that what you have created is a capacitor, i.e. two copper surfaces with a dielectric in the middle. Now this specific setup would give you ~83[pF] of capacitance. At this point you could think to yourself, well that is a tiny amount of capacitance which will get lost in my PDN. This is somewhat true, however, keep in mind that this is a large copper plane delivering this capacitance, meaning the internal resistance and inductance of this capacitor is very small. Inductance and resistance of copper planes is proportional to the number of squares in your signal path. This means that the capacitor, whilst being small in value, is the closest you can get to an ideal capacitor on a PCB (ignoring any via resistance or inductance).

Now that we know it is a good feature, how can we then manipulate our stackup to create a higher capacitance? A capacitor’s capacitance is proportional to the distance between the planes, the area of the planes, and the dielectric constant of the centre material. The board size (therefore most often the area of the planes) is usually dictated by other factors and is therefore most often off limits. The dielectric constant is something which is fairly similar and won’t vary too much, even with different PCB materials. Therefore, the answer is simple, shrink the gap between the two planes. In a four layer stackup you have two ways to achieve this: either reduce the board thickness (which could add cost, or be impossible due to mechanical constraints) or increase the gap between your signals and reference planes (this has undesirable effects such as increased radiated emissions due to less controlled electric fields, fatter traces for impedance matching, and more). Because of those reasons I would advise to opt for option three, which is to add more layers to your stackup. So let’s have a look at a six layer stackup.

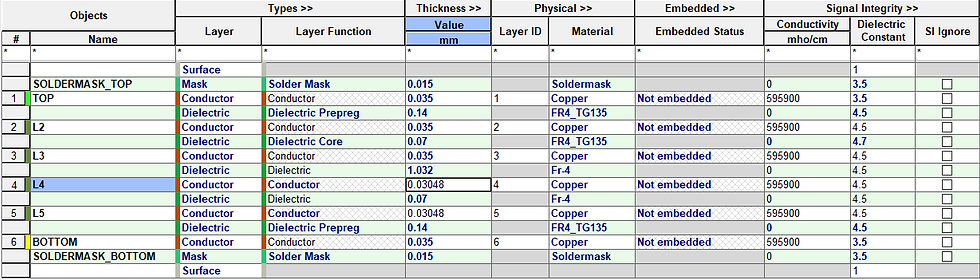

Above you can see a 6 layer stackup. Below you can see the thickness details I have gone for.

As you can see the distance between L2 and L3 is now much shorter, in fact it is roughly the thickness of one 1080 prepreg of FR4. The same distance can be found between L4 and L5. The effect of this is a much higher capacitance, resulting in ~1.4[nF] for each plane pair. If you wanted to go all out you could even use both L2/L3 and L4/L5 as power planes, effectively doubling your capacitance (among other benefits such as shorter power vias).

In practice you will rarely want to do this on a 6 layer board as most of the time the reason for a 6 layer board is not to improve your PDN in this way. You might however want to do it once you have more layers to play with, i.e. 8 or 10 layers (more commonly one plane pair is used for one power/GND plane and the other for a different power net).

Now that we have established some basic knowledge about planes and stackups we can marry it up to the answer that we gave at the top of this section. A closely coupled power plane is an “ideal” capacitor embedded into your PCB stackup.

Power delivery networks

The second question of why we care is a slightly trickier one and it relates to PDNs. We will go through a very brief overview of PDNs, with some simplifications, to allow us to understand the subject enough for our discussion of closely coupled power planes.

PDNs are designed to deliver surge currents that occur at higher frequencies than the power supply unit (PSU) can supply. Technically the PSU is part of the PDN, but in our discussion we will assume that at some arbitrary frequency, say 100 [kHz], infinitely large current surges can be supplied without issue. It is then a concern for the designer of the PCB to look at any high frequency switching circuits, e.g. processors, and determine their frequency response requirements of the power rail. For certain integrated circuits (ICs), e.g. larger processors and FPGAs, this is often supplied in the form of a table of different frequency bands and maximum impedance at those. In other cases this might be less straight forward, but estimations can always be made by educated guesses using the maximum switching current and their frequencies coupled with the voltage tolerances on the power rails of the ICs in question. Generally speaking, if it is not specified it is probably not of much concern, if it is specified make sure you understand it and apply best practices. The frequency ranges in question are most often <50[MHz] but can go up to 100[MHz]. Anything above that quickly becomes impossible to achieve on a PCB using components. This is due to the parasitic elements within the components on the PCB, e.g. typical 10nF X7R 0402 capacitors will become inductive at ~100[MHz] and therefore not produce any help in reducing your impedance. It is worth noting that you should always use the worst possible tolerance, i.e. if one IC has a target impedance of 100mΩ, and another one 150mΩ, you must use the lower.

At this stage the designer will have a target impedance to design to. This is generally done by adding bulk capacitors, decoupling capacitors, and (hopefully after reading this blog) closely coupled power planes. These components will provide the low impedance current source that the IC needs. The PDN can be modelled reasonably using the schematic below and, in applications where it is crucial, a network analyser can be used to verify the simulation. There are many more considerations that come into play for PDNs, but we will leave them for another time.

To quickly review what is seen on the schematic and its frequency response. Each of the capacitors represents a number of parallel capacitors, these are modelled as non-ideal with the parasitic values added externally. C5 is modelled as an ideal capacitor, and this represents our closely coupled power planes. In the results the red line is an arbitrary impedance target of 100mΩ, and the plot is over the frequency range of interest plus one decade in either direction. In the example produced the target is met with ease and the amount of capacitors used could therefore be reduced during optimisation. It is worth noting that the parasitic values mentioned in the schematic are not accurate and should be replaced by what your specific capacitors will have. It is also worth noting that this value is effectively the combination of the inductance of the via (if applicable), trace, and parasitic inductance of the capacitor, the same goes for the resistance.

Having a 1-5[nF] ideal capacitor provides a very high frequency decoupling operation, allowing much better power integrity and more reliable operation of the whole PCB. It will also very likely improve EMC performance, as any noise on the power plane will be reduced, which generally gets emitted from the board through any external connection. Because of this closely coupled power planes are an extremely desirable feature on any high-speed electronics.

Summary

In summary, we have defined what closely coupled power planes are, i.e. planes which are positioned close enough to each other that they are significantly capacitively coupled. We have also quickly touched on why this is desirable to use on PCBs, i.e. improved power integrity, low impedance at high frequency on our PDN, and likely improved EMC performance.

While writing about this subject I realised that it is a subject which requires quite a lot of specific knowledge to grasp. Here at Sleipnir Electronics we want to try and share knowledge and are happy to further discuss this with you, simply drop us an email or comment. We will hopefully also include further posts soon about the subjects which would be useful to know when reading this post and might even delve deeper into the realm of PDNs at some point.

Until next time!

Atli

Comments